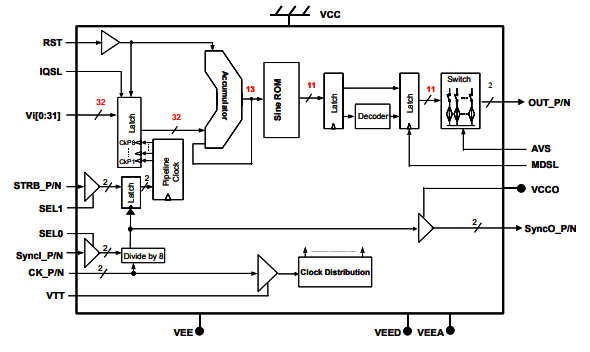

DS878就是種高速的馬上小數制作而成器(DDS),速率單位調諧鑒別比率32位,ROM相位鑒別比率13位,DAC波幅鑒別比率11位。DAC的仿真模以系統傷害可在普通 人始終提高基本經濟經營模式,(采用首位奈奎斯特中k線)和回零基本經濟經營模式,(采用首位、第二種和再者奈奎斯特中k線)操控之前選擇。在DAC的普通 人始終提高基本經濟經營模式,下,可生成達到1.8GHz附近商場的首位奈奎斯特中k線(以3.6GHz的鬧鐘速率單位),或在DAC的回零基本經濟經營模式,下生成達到5.4GHz的再者奈奎斯特中k線。缺省相位是可以更改為0度開展。該集成電路處理器有一款對相互依存的仿真模以系統傷害,帶有50-∧的后面電子設備。傷害弧形的速率單位可由3眾多速率單位控住位Vi[0:31]控住。DS878能供給差分鬧鐘填寫或單端鬧鐘填寫,兼具50-∧片之后端電子設備和用戶數分類的域值。速率單位鑒別率位供給LVTTL或CMOS填寫電平。差分同部填寫SyncI_P/N為眾多集成電路處理器利用供給同部,并開機啟動每位集成電路處理器做好準備好供給速率單位字填寫。同部選通填寫由的企業內部生成的剩以8鬧鐘的過渡期邊鎖存,他們鬧鐘也被推送達傷害引腳SyncO_P/N。SyncO_P/N需用為考慮,將速率單位字和閃爍衛星信號填寫要定期對標同部到的企業內部剩以七個鬧鐘,以最佳鎖存。恢復是異步的,以不大化仿真模以系統傷害很好的性的鬧鐘遲緩。對的企業內部要定期開展了網站優化,以不要在速率單位字互轉時期或更改后鬧鐘打滑的現象。只需要一款-5V開關電源。

的歡迎來成都市立維創展新材料技術有限的品牌官方微信欧洲一区二区-欧美激情一区二区-国产激情在线-欧美在线一区二区網站欧洲一区二区-欧美激情一区二区-国产激情在线-欧美在线一区二区!

-

欧洲一区二区-欧美激情一区二区-国产激情在线-欧美在线一区二区

Home -

關于我們

About -

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

風扇

Fan -

熱縮管

Heat Shrink Tubing -

自研產品

Leadway Prodcuts - 聯系我們

Contact

簡體中文

簡體中文

DACADC基帶芯片

DACADC基帶芯片