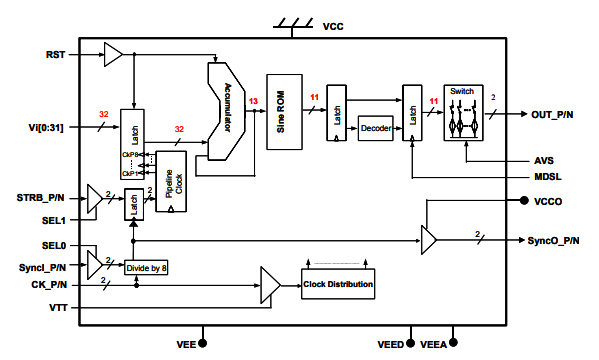

DS872是一種種高速度直接性數字6煉制器(DDS),頻次調諧糞便率有32位,ROM相位糞便率有13位,DAC波動糞便率有11位。DAC的模以網打印轉型可在正常人人始終維持機制(選用在首要奈奎斯特股票k線)和校準機制(選用在首要、2和最后奈奎斯特股票k線)實際操作左右兩會選擇。余弦波可在DAC正常人人始終維持機制下引發達到了1.5 GHz附進的首要奈奎斯特股票k線(以3 GHz的鬧鐘速率單位),或在4.5 GHz左右兩引發達到了最后奈奎斯特股票k線(DAC校準機制)。初期相位不錯從置為0度逐漸開始。該集成ic有個對互補式的模以網打印轉型,極具50Ω的背部POS機移動終端。打印轉型正弦波形的頻次可由35個頻次管理位Vi[0:31]管理。DS872認可差分鬧鐘填寫或單端鬧鐘填寫,并極具50Ω片上之后端POS機移動終端和我們概念的域值。頻次糞便率位認可LVTTL或CMOS填寫電平。差分數據同歩填寫SyncI_P/N為各個集成ic選用保證數據同歩,并起動每隔集成ic注意好認可頻次字填寫。數據同歩選通填寫由內外引發的剩以8鬧鐘的作為銜接邊鎖存,他們鬧鐘也被發送信息到打印轉型引腳SyncO_P/N。SyncO_P/N用于為學習,將頻次字和自閃無線信號填寫要定期對與內外divideby-8鬧鐘數據同歩,以恰當鎖存。校準是異步的,以較小化模以網打印轉型合理性的鬧鐘推遲。對里外要定期開始了整合,以應對在頻次字轉型期間內或從置后鬧鐘脫鏈。只需要是一個-5V電源開關。

喜愛來成都市立維創展新材料技術有現廠家公司企業網站!

-

欧洲一区二区-欧美激情一区二区-国产激情在线-欧美在线一区二区

Home -

關于我們

About -

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

風扇

Fan -

熱縮管

Heat Shrink Tubing -

自研產品

Leadway Prodcuts - 聯系我們

Contact

中文版

中文版

DACADC電源芯片

DACADC電源芯片